# Z1013-128

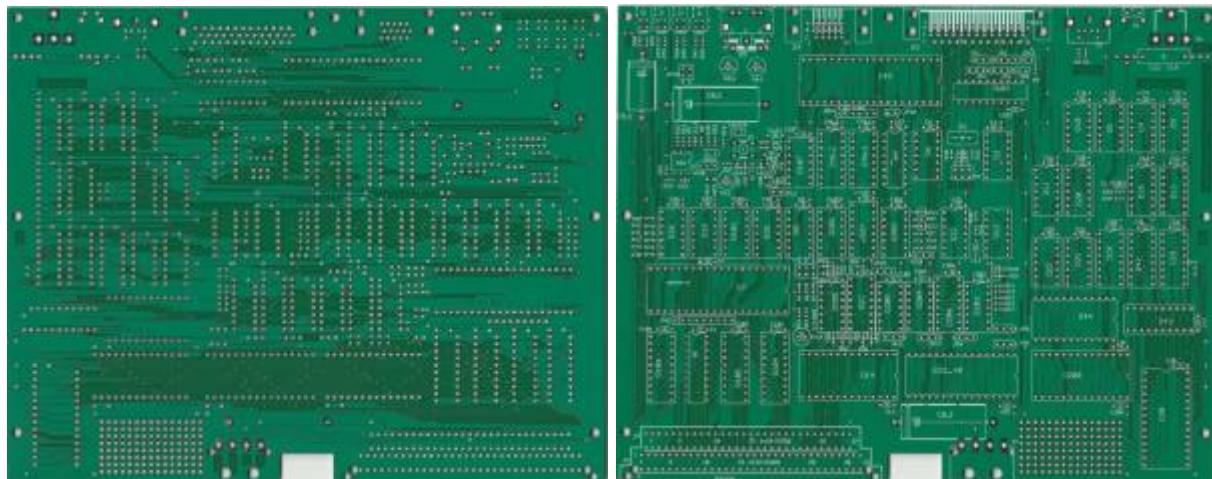

Der Z1013-128 ist eine Entwicklung aus dem Jahr 2016.

Der Rechner ist ein Z1013 mit 128K sRAM (zwei 64k-Blöcke) und auf einer Platine von der Größe einer K1520 Leiterplatte platziert. In der Grundfunktion ist er bis auf den HF-Ausgang 100% hard- und softwarekompatibel zur Urversion.

<http://www.robotrontechnik.de/html/forum/thwb/showtopic.php?threadid=13852>

Der Z1013-128 hat folgende Neuerungen :

1. erst einmal voll kompatibel zum Z1013-64

2. getriebener Daten-, Adress- und Steuerbus am Steckverbinder

3. vollständige Dekodierung der I/O-Adressen

4. 128kB sRAM ,softwareseitige Umschaltmöglichkeit zwischen zwei 64k-Bereichen

5. Anschlussmöglichkeit einer PS/2-Tastatur nach Gubsch

6. verschiedene Monitore über Jumper aus wählbar( jeweils 4k F000-FFFFh )

7. 32k Eprom softwareseitig zu und abschaltbar auf der oberen 32k

8. über diesen 32k EPROM ist der Start von DVU o.ä. mit einem Jump-Befehl möglich

9. /MEMDI-Steuerung von 128k sRAM und 32k-EPROM

10. teilkompatibel mit der Peters-Platine ( D4=BS-OFF, Abgriff der 4 FF-Signale aus D4-D7 möglich )

11. Rückmeldung der FF-Stellung über LED

12. optimierte RESET-Schaltung ( Verknüpft mit /M1 )

13. wahlweise auch Internes RESET=Bus-RESET (z.B. für Color-BWS, VIS3 usw. notwendig )

14. der X1 Stecker (Busstecker) kann mit 2x29 EFS oder 2x32DIN bestückt werden

15. der USER- und Tastaturausgang kann auch wahlweise mit SUB-D oder mit EFS Stecker oder Buchsen bestückt werden

Der Prototyp läuft aktuell z.B. mit folgender Hard-/Software-Konfiguration:

- batteriegepufferte RFL 2x256k nach MP3/88 auf 98h und 58h (bzw. mindestens eine auf 98h)

- Color-BWS ab E800h auf 10h (grün/schwarz), 32x32/BS oder 64x32/SCP (neuer CPLD von

Heiko)

- DVU/USB ab A000h auf DC-DFh (im 32k-Eeprom zum Umladen/Starten mit „JUMP FF40“)

- Monitor 2.02 (zzgl. Sprungverteiler, Druckertreiber S3004-A0/A1 und Umladeprogrammen)

- PS/2-ATtiny2313-Programm für Monitor 2.02

- angepasstes SCP 2.2 ab C800h (im 32k-Eeprom zum Umladen/Starten mit „JUMP FF70“)

- GIDE auf freier I/O-Adresse

Für die Serienvariante aus dem Forum ist die aktuelle Dokumentation hier auf dieser Webseite zu finden.

## Downloads

- z1013\_128\_doku.rar

Sämtliche Unterlagen (Schaltplan, Bestückung, ROMs, ...)

- zusatzplatine\_doku\_v1.zip

Unterlagen zur Zusatzplatine

## Aufbauhinweise

aus dem Forum zusammengeklaubt ...

- S2 ist ein vertikaler Kurzhubtaster für eine Frontbedienung des RESETs! Ist parallel zu S1 geschalten. TASTER 3305B Kurzhubtaster 6,6×7,4mm,Höhe:8,35mm,12V,horiz, bei Reichelt

- JP15 ist da die Beschriftung anders?

Bitte am aktuellen Bestückungsplan orientieren! Die Jumperstellungen sind ausschließlich aus dem Schaltplan entnommen. Bei der nächsten Serie müssen wir den Bestückungsaufdruck korrigieren.

- LED Blöcke von Reichelt/Pollin, kann das sein, das die LEDs verkehrt rum eingesetzt sind? also Kathode und Anode getauscht?

Beim 2. Prototypen wurden diese LED-Blocks verwendet:

<https://www.conrad.de/de/de/led-baustein-gruen-rot-l-x-b-x-h-1334-x-11-x-432-mm-dialight-553-0121f-1126700.html>. Wenn man ins Datenblatt schaut, liegt die Kathode rechts und die Anode

links bei Blick auf die LED von vorn. Also alles korrekt zur aktuellen Platine. Bei Reichelt ist es genau anders herum!

- bitte beachten, daß statt dem in der Stückliste enthaltenen AT90S2313 ein ATtiny2313-20PU oder ATtiny2313A-PU genommen wird. Sollte sich jemand finden, der das vorhandene PS/2-Programm auf einem AT90S lauffähig bekommt, dann wäre dieser Hinweis hinfällig.

- JP12 leitet das interne Reset (also das Boardreset) auch auf den Bus, was z.B. beim Betreiben einer VIS3 oder Heiko's BWS notwendig ist, um diese Module in den Grundzustand zu setzen. Sollte das bei einer anderen Anwendung stören, muß er offen bleiben (wir wollten alles so flexibel wie möglich halten).

- JP10 ist aus dem Original-Z1013 übernommen. Er verbindet den PIO-Ausgang B6 mit dem Magnetband-Interface.

- J15 wird aber in Matthias seiner Liste mit 1-2 geschlossen angegeben und 3-4. Die 1-2 Beschriftung an der Platine irretiert da, da die 1 und 2 nicht die Pins zum Brücken sind. Jumperbeschriftung für den Takt verkehrt ist? Es ist ja 4-2-1 die MHz-Angabe ist vertauscht. Jörg weiß schon Bescheid und korrigiert das im Schaltplan und auf der Platine. Das war 1:1 vom Original-Schaltplan übernommen, wo die Zuordnung auch schon nicht stimmt.

- Wir haben mit JP16 und JP20 die Möglichkeit geschaffen, den 761er auch ohne die -5V zu betreiben. Allerdings sind ggf. Umbauarbeiten nötig (s.u.)

## Kassetteninterface

mögl. Lösungen

a) -5V mit U7660 erzeugen, s. Forumsbeitrag [348]

- b)

1. R24 durch eine brücke ersetzen.

2. pin 4 vom OPV an Masse (0V)

3. R21 von Masse lösen und auf Spannungsteiler 10k/10k legen und die 2.5v mit 100nF abblocken. Rest bleibt wie er ist.

c)zusätzlich noch BAT-Diode

außerdem: nur den linken Kanal verwenden, sonst verursachen phasenverschobene Signale Probleme.

## Jumper

```

JP1 Monitorauswahl für PS/2:

1-2 geschlossen 2.02. Monitor

default

2-3 geschlossen Brosig-Monitor (angepaßtes ATtinyprogramm notwendig!)

JP2 Monitorauswahl für PS/2:

1-2 geschlossen 2.02. Monitor

default

2-3 geschlossen Brosig-Monitor (angepaßtes ATtinyprogramm notwendig!)

```

JP3 Monitorauswahl für PS/2:

1-2 geschlossen 2.02. Monitor

default

2-3 geschlossen Brosig-Monitor (angepaßtes ATtinyprogramm notwendig!)

JP4 Monitorauswahl für PS/2:

1-2 geschlossen 2.02. Monitor

default

2-3 geschlossen Brosig-Monitor (angepaßtes ATtinyprogramm notwendig!)

JP5 Monitorauswahl für PS/2:

offen 2.02. Monitor

default

geschlossen Brosig-Monitor (angepaßtes ATtinyprogramm notwendig!)

JP6 Umschaltung 64k Low / 64k High:

2-3 geschlossen 64k High kann mit FlipFlop D202/G1 (D6) aktiviert werden default

1-2 geschlossen 64k High kann nicht aktiviert werden

JP7 Taktfrequenzauswahl:

3-4 geschlossen 2 MHz

default

1-2 geschlossen 1 MHz

5-6 geschlossen 4 MHz

JP8 Definition Resetzustand:

1-2 geschlossen 32k Eprom ist nach Reset inaktiv default

2-3 geschlossen 32k Eprom ist nach Reset aktiv

JP9 Definition Resetzustand:

2-3 geschlossen Bereich EC00-FFFFh (BWS+Monitor) nach Reset aktiv default

1-2 geschlossen Bereich EC00-FFFFh (BWS+Monitor) nach Reset abgeschalten

JP10 geschlossen

default

JP11 Einblendung 32k Eprom:

1-2 geschlossen 32k Eprom kann mit FlipFlop D203/G1 (D5) aktiviert werden default

2-3 geschlossen 32k Eprom kann nicht aktiviert werden

JP12 leitet Z1013-Reset auf den Bus:

geschlossen internes Reset auch auf den Bus

default

offen kein internes Reset zum Bus

JP13 Spannungsversorgung X2/Tastatur:

offen Anschluß X2C13 frei (bei Verwendung von EFS-Buchse)

default

geschlossen Anschluß X2C13 auf +5V (da kein A13 an SUB-D)

JP14 Auswahl von 4k Monitorbereichen:

Eprom 2764 ab 0000h ab 1000h (X = geschlossen/Low, 0/- =

offen/High)

1-2 geschlossen X 0

3-4 geschlossen - -

5-6 geschlossen - -

Eprom 27128 ab 0000h ab 1000h ab 2000h ab 3000h

1-2 geschlossen X 0 X 0

3-4 geschlossen - - - -

5-6 geschlossen X X 0 0

Eprom 27256 ab 0000h ab 1000h ab 2000h ab 3000h ab 4000h ab

5000h ab ...

1-2 geschlossen X 0 X 0 X

0 X

3-4 geschlossen X X X X 0

0

5-6 geschlossen X X 0 0 X

X 0

JP15 Zustandssignalisierung:

1-2 geschlossen /WR als Aktivitätsanzeige des Z1013

default

3-4 geschlossen Anzeige für +5V-Spannungsversorgung

default

JP16 Anpassung der OPV-Spannung:

offen sobald JP20/1-2 geschlossen (-5V)

default

geschlossen sobald JP20/2-3 geschlossen (Masse)

JP17 Zeichensatzumschaltung:

2-3 geschlossen IBM-ZS kann mit FlipFlop D202/G2 (D7) aktiviert werden

default

1-2 geschlossen IBM-ZS kann nicht aktiviert werden

**JP18 Definition Resetzustand:**

1-2 geschlossen IBM-ZS ist nach Reset inaktiv

default

2-3 geschlossen IBM-ZS ist nach Reset aktiv

**JP19 Definition Resetzustand:**

1-2 geschlossen RAM 64k High ist nach Reset inaktiv

default

2-3 geschlossen RAM 64k High ist nach Reset aktiv

**JP20 Anpassung der OPV-Spannung:**

1-2 geschlossen -5V

default

2-3 geschlossen Masse

## Zusatzplatine

### Zusatzplatine für K1520-Systeme

Um Modulplätze in den Rechnern einzusparen, hat Jörg L. eine Leiterplatte entworfen, wo die Komponenten BWS(VGA), 2x 256k-sRAM-Floppy, GIDE, RTC, USB und LAN vereinigt sind. Dazu wurden bereits vorhandene Schaltungen (z.T. modifiziert) zusammengefügt. An dieser Stelle noch einmal herzlichen Dank an die Entwickler dieser Einzelschaltungen, ohne deren Arbeit diese neue Platine nicht möglich gewesen wäre. Das Gleiche gilt für die übernommene Software. Die Prototypen der neuen Zusatzplatine wurden von Matthias H. aufgebaut und bis 4MHz getestet.

Vorserienplatine

<http://www.robotrontechnik.de/html/forum/thwb/showtopic.php?threadid=16166>

Im Download Zusatzplatine Doku\_V1.ZIP (s.o.) befindet sich die Dokumentation zur aktuellen Platine sowie die Software. Aufgrund der vorhandenen Möglichkeiten bezieht sich diese teilweise auf den Z1013-128, kann aber anhand der beigefügten Quellen sowie bekannten Beschreibungen der Einzelkomponenten an andere Bedingungen angepasst werden.

Bei Fragen zum Aufbau und der Software gern über das RobotronTechnik-Forum melden.

„Jörg“ und „Lötspitze“

From:

<https://hc-ddr.hucki.net/wiki/> - Homecomputer DDR

Permanent link:

<https://hc-ddr.hucki.net/wiki/doku.php/z1013/z1013-128?rev=1572949758>

Last update: **2019/11/05 10:29**