2025/11/05 14:34 1/6 RAM-Floppy

# **RAM-Floppy**

"RAM-Disks sind nützliche Einrichtungen, die wohl besonders von denjenigen sehr geschätzt werden, die an Rechnern mit Kassettenbandspeichern ihre Geduld üben müssen. Aber auch im Vergleich zur Diskette kann die RAM-Disk erstaunliche Geschwindigkeit bieten. Wer schon einmal in längeren Assemblerquellen mit einem Textverarbeitungsprogramm wie TP herumgesucht hat, weiß ein Lied davon zu singen."

# 256K

# mp3/88 - präcitronic

Bilder s.a. http://www.robotrontechnik.de/html/computer/z1013 ausbau.htm

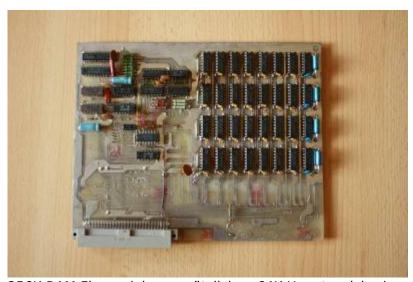

256K-RAM-Floppy (ohne zusätzlichen 64K Hauptspeicher)

in der mp 3/88 wurde von Wolfram Kammer und Wolfgang Spindler eine K1520-kompatible RAM-Disk mit 256K Speicherplatz und zusätzlich 64K Hauptspeicher vorgestellt. Diese Platine wurde kurz darauf von präcitronic (IH Mittweida) produziert. Rainer Brosig steuerte die Anpassung an den Z1013 bei; als Software gab es HEADERDISK, ein Headersave-kompatibles Programm, mit dem die RAM-Disk als Kassettenrekorderersatz genutzt werden konnte. Die zum Anschluß an den Z1013 notwendigen Hardwareänderungen und die Software zum Betrieb max. zwei dieser RAM-Disk wurde in einem Heftchen von "hobby electronic Dresden" beschrieben.

Durch die Veröffentlichung in einer Zeitschrift und die Bezugsmöglichkeit einer industriell gefertigen zweiseitigen nichtdurchkontaktierten Leiterplatte hat diese RAM-Disk eine gewisse Verbreitung gefunden.

#### Downloads:

- mp3-88-raf.pdf Artikel der mp

- praecitronic.pdf Beschreibung zur Platine

- raf256.zip Software dazu

Last update: 2017/12/13 11:52

• z1013-raf.pdf Anpassung an Z1013

raf256vp.zip

universeller nachladbarer Treiber für max 2 RAF256 auf Adressen 98 und 58 (vp170308)

#### Ansteuerung:

Zum Adressieren von 256 KByte werden 18 Adreßbits benötigt. Die niederwertigsten 8 Bit stellt ein vom Programm mittels OUT-Befehl ladbarer Adreßzähler (2 x 74LS193) bereit. Die nächsthöheren 8 Bit müssen vom Programm in ein Oktallatch (DS8282) geladen werden. Die restlichen 2 Bit stecken in der Peripherieadresse, unter der das Bedienprogramm anschließend die RAM-Disk liest oder beschreibt. Nach jedem Zugriff inkrementiert die Zugriffslogik der RAM-Disk den o. g. Adreßzähler. Damit sind INIR- und OTIR-Befehle für das Umladen der Daten bestens geeignet. Die RAM-Disk belegt insgesamt 8 E/A-Adressen nach folgendem Schema:

## Grundadresse plus

0 = Lesen/Schreiben Bank 1

1 = Lesen/Schreiben Bank 2

2 = Lesen/Schreiben Bank 3

3 = Lesen/Schreiben Bank 4

4 = nicht benutzen

5 = nicht benutzen

6 = mittlere 8 Adreßbit laden

7 = niedrigste 8 Adreßbit in den Zähler laden.

Die Grundadresse kann man in gewissen Grenzen frei wählen, indem man das Wickelfeld D entsprechend verdrahtet. Am Z1013 üblich sind

```

DB 98H ;GRUNDADRESSE DISK A

DB 58H ;GRUNDADRESSE DISK B

```

#### Aufbauhinweise:

Auf der Platine der RAM-Floppy von PRÄCITRONIC Dresden fehlen zwei Leiterzüge auf der Leiterseite. Von Schaltkreis D5 und D7 (D 195) sind jeweils PIN 11 mit einem Draht zu verbinden. Der Leiterzug /RESET führt nicht durchgehend zu den Schaltkreisen (Steckverbinder A 20). practic 2/89, S. 88-89

Umbau auf 512K: practic 1/90, S. 39-40

2025/11/05 14:34 3/6 RAM-Floppy

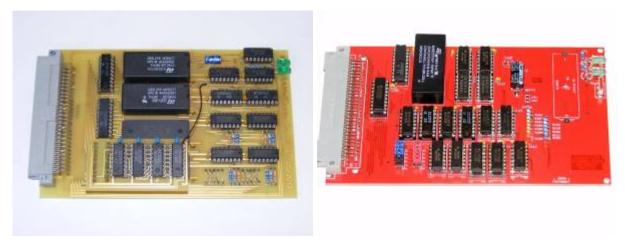

## Nachbau 2x 256k MHC

Matthias H./MHC "Lötspitze"

links 2x256K-RAM-Floppy mit 128k IC´s, rechts 2x256K-RAM-Floppy mit 512k IC (Variante mit ZeroPowerRAM)

Diese RFL's sind softwareseitig zu 100% präcitronic-kompatibel nach MP 3/88. Link zum Forum: http://www.robotrontechnik.de/html/forum/thwb/showtopic.php?threadid=9522

#### Download

• Unterlagen: raf256k\_mhc.zip

• Schaltplan mhc\_2x256k-rfl.pdf

• Schaltplan mit 512K RAM mhc-jl 2x256k-rfl.zip (170402)

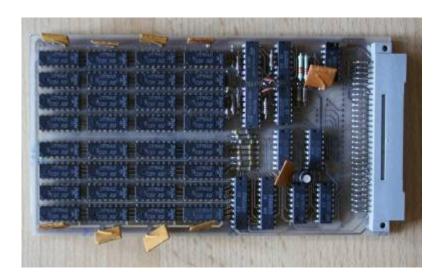

## Dresden

Unterlagen? Ist diese Karte kompatibel zur mp3/88?

# Last update: 2017/12/13 11:52

#### **NANOS**

Die RAM-Karte BG-Nr. R1.1-03/2 des NANOS-Systems der Ingenieurhochschule f. Seefahrt Warnemünde hat eine Kapazität von 256K. Dieser Speicher kann wahlweise als 256K-RAM-Disk oder als 192K-RAM-Disk und 64K Hauptspeicher arbeiten.

Mir standen 1990 2 RAM-Floppies des NANOS-Systems zur Verfügung. Dafür habe ich einen HEADERDISK-kompatiblen Treiber geschrieben, die Verwaltungs-Oberfläche UNICOPY angepasst und zum Betrieb unter CP/A auch die nötigen BIOS-Treiber. Genutzt wurde das vom damaligen Computerclub Sanitz (Leiter T. Witza).

#### Arbeitsweise:

Bei Aktivierung wird ein 256 Byte großer Bereich in den Arbeitsspeicher des Rechners eingeblendet.

Standardadressen meiner RAM-Floppies:

| DB | 0C4H   | RAMDI  | Speicher aus          |

|----|--------|--------|-----------------------|

| DB | 0C5H   | RAMEN  | Speicher ein          |

| DB | 0C6H   | READDI | Lesen gesperrt        |

| DB | 0C7H   | READEN | Lesen freigeben       |

| DB | 0C0H   | LDAH   | High-Teil der Adresse |

| DB | 0C2H   | LDBB   | Bankauswahl           |

| DA | 0F700H | WINDOW | Fensterbereich        |

Die Adressen werden über PROMs 74S287 festgelegt und sind daher ohne geeigneten Brenner nicht so leicht zu ändern.

→ http://buebchen.jimdo.com/8-bit-selbstbau/andere-eprommer/ hat Unterlagen zu einem solchen Brenner.

2025/11/05 14:34 5/6 RAM-Floppy

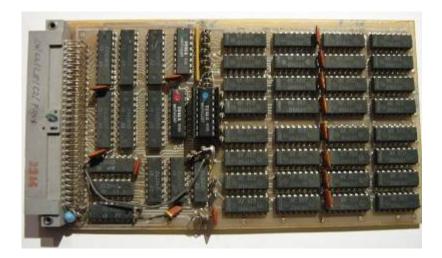

# 2048 k

## **RAF2008**

K1520-I/O Platine mit zwei Port-Adressen

Beschreibung s. RAM-Floppy RAF2008

Die zur Ansteuerung nötige Adresse wird ähnlich wie bei der RAM-Disk nach mp3/88 gebildet:

- Raf\_C = RAF-Control Port zum Laden der Track- & Sector-Adresse "HiAdr" via D-bus 0...7 und A-bus 8...14 (B-Reg).

- Raf\_D = RAF-Data-I/O Port zum Schreiben/Lesen von max. 128 zusammenhängenden Bytes mit einem INIR-/OTIR-Befehl mit einem 7-bit Byte-Index "LoAdr" auf dem A-bus 8...14 (B-Reg)

```

:---- Vollständige 19 bit RAM-Adresse (1 RAF 512) -----:

7: 6 5 4 3 2 1

0:

15 14 13 12:11 10 9 8 7 6 5 4 3 2 1 0:

B-Register !!

r-Register

+--+--+--+--+--+

! !!!!! !

7: 6 5 4 3 2 1

! für

! OUT(C),r-Befehl !

+--+--+--+

!__auf_Ctrl-Adr___!

! >512k !

!//: B-Reg (INIR/OTIR) !

+--+--+--+

A0V

Adressüberlauf-Bit (RAF 512)

! oberer Adr.bus in !

(Bit 10 bei RAF 128)

! INIR-/OTIR-Befehl !

PR0T

!_____!

Zugriffsschutz-Bit (1=geschützt)

```

Die In-Sektor-Adressen (LoAdr 6...0) entsprechen dem B-Register bei OTIR/INIR, so daß die Bytes innerhalb eines Sectors in fallender Reihenfolge gespeichert werden (B beginnt mit 128 bzw. 127)!

Last update: 2017/12/13 11:52

From:

https://hc-ddr.hucki.net/wiki/ - Homecomputer DDR

Permanent link:

https://hc-ddr.hucki.net/wiki/doku.php/z1013/module/raf?rev=1513165926

Last update: 2017/12/13 11:52