Inhaltsverzeichnis

Reset-Logik

Bei der originalen Reset-Beschaltung kann es zu Veränderungen im Speicher kommen, da kein Refresh erfolgt. Um das zu verhindern, muss das Reset-Signal mit M1-Signal verknüpft werden.

Hier werden drei Lösungen vorgestellt, die Abhilfe schaffen:

mit DL002

Ich kann leider nicht mehr sagen, woher ich die nachfolgende Schaltung habe. auf jeden Fall ist sie aber an meinem Z1013 im Einsatz. Benötigt werden ein DL002, eine Germanium-Diode, ein Widerstand und ein Kondensator. Das ganze wird huckepack auf A26 aufgelötet.

Empfehlung der IG HC

Es ist das RESET-Signal mit M1 zu s y n c h r o n i s i e r e n. Leitung zwischen R 17/C 1.11 und A 25/PIN 10 auftrennen, auf einen Eingang eines Gatter des DL 032 (OR-Gatter) legen, zweiten Eingang mit M1 (PM1) verbinden, Ausgang auf A 25/PIN 10 legen.

Wichtig ist hier aber ein AUTO-RESET. Nach R. Brosig ist mit einem A 302 am Ausgang des A 24/PIN 2 (zu StB 4) ein etwa 1 sec langes Low-Signal zu legen. A 302/PIN 4 an A 24/PIN 2, A 302/PIN 2 mit R (100k-Ohm) an 5P und C (Elko ca. 10myF/16V) an Masse.

FA 6/88, S. 276

S. GÜNTHER – Y35XN, Dr.-Ing. U. HINZ: Resetlogik für den „Z1013“

Mittlerweile hat der Mikrorechnerbausatz „Z 1013„ vom VEB Robotron-Elektronik Riesa einen breiten Freundeskreis gefunden. So ist auch seit Frühjahr 1986 bei den Autoren je einer dieser Rechner in Betrieb. Allerdings machte sich schon von Anfang an ein Mangel an unseren und evtl. auch weiteren Exemplaren bemerkbar. Nach dem Betätigen der RESET-Taste kommt es oft zu Zerstörungen des aktuellen RAM-Inhalts. Nach Meinung der Autoren existiert dafür folgende Ursache: Das RESET-Signal wird während eines Speicherzyklus nicht gesperrt. Zu beachten ist, daß der RFSH-Zyklus Teil des Lesezyklus M1 ist. Aus diesem Grund kann ein begonnenes Auffrischen der dynamischen RAM-Zellen abgebrochen werden, was für die gerade angesprochene RAM-Zeile ein zerstörendes Auslesen der Tnformation zur Folge hat.

Um nun diesen Nachteil zu beseitigen, wurde eine Anregung aus der Literatur aufgegriffen [1]. Die dort beschriebene Schaltung sollte einen RESET nur während eines M1-Zyklus erlauben. Leider ist diese Schaltung in ihrer Ursprungsform für den „Z 1013“ nicht brauchbar, da der Rechner nach dem Einschalten kein Power-On- RESET, also keinen Kaltstart durchführt. Die oben angeführte Schaltung blockiert sich, da M1 nach dem Einschalten passiv bleibt. Erst eine geeignete Power-On- RESET-Schaltung würde den Grundgedanken aus [1] zur Wirkung kommen lassen. Übliche Power-On-RESET-Schaltungen nutzen eine RC-Kombination, deren Zeitkonstante größer als die Einschaltzeit der Netzspannung ist. Der so entstehende Impuls wirkt direkt auf den RESET-Eingang des Prozessors. Allerdings ist diese Variante auf den „Z 1013„ nicht anwendbar, da dem entsprechenden Pin des Mikroprozessors das Kaltstartflipflop A25/A26 vorgeschaltet ist. Durch einen Low-Impuls kann es gesetzt werden. Nach dem Einschalten des Rechners fehlt dieser Impuls jedoch. Erst das Betätigen der RESET-Taste bringt den Rechner in den definierten Anfangszustand. Selbstverständlich hat ein Low-Impuls auf der RESET-Leitung (A20) des Bussteckverbinders die gleiche Wirkung. Zu bemerken sei noch, daß das Rechner-RESET original nicht auf den Bus wirkt, wodurch eventuell vorhandene Zusatzbaugruppen nicht zentral rückzusetzen sind.

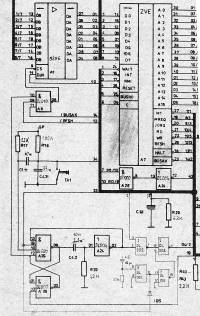

Um alle o. g. Nachteile zu beseitigen, schlagen die Autoren folgende Lösung vor: Das extern erzeugte RESET-Signal muß mit M1 und MREQ logisch verknüpft werden. Es ist nur weiterzuleiten, wenn M1 aktiv (low) und MREQ inaktiv (high) ist. Mit anderen Worten: Ein RESET wird nur dann zugelassen, wenn der Prozessor einen Befehlskodelesezyklus (M1) durchführt und die Speicher nicht anspricht. Bild 1 soll das deutlich machen. Dynamische Speicherzellen sind somit vor unvollständigen Speicherzyklen geschützt. Ein Rücksetzendes Rechners ist dennoch immer möglich, da Befehlskodelesezyklen ständig auftreten.

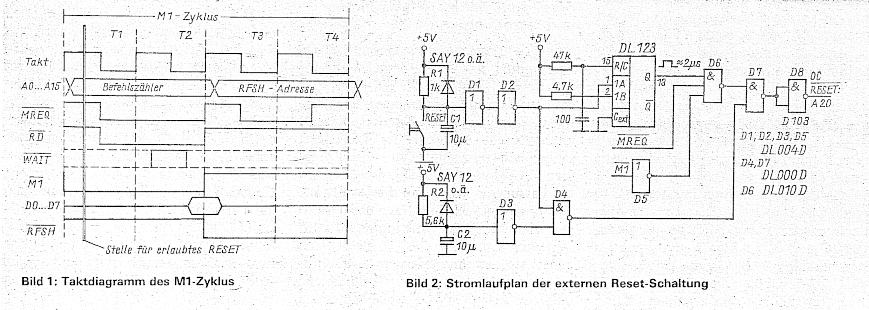

Bevor jedoch nun das externe RESET in beschriebener Art und Weise generiert werden kann, ist das anfangs schon erwähnte Rücksetzen im Einschaltmoment nötig. Dies entsteht aus zwei unterschiedlich verzögerten Power-On-Signalen. Beide Signale liegen an den Gattern D1 und D3 vor. Mit D4 werden sie so verknüpft, daß nach dem Anliegen der Betriebsspannung ein Low-Impuls von ungefähr 40 ms Länge entsteht. Dieser Impuls gelangt an das Gatter D7, das ihn mit dem extern beeinflußbaren RESET logisch verknüpft. Das nachgeschaltete Open-Collector- Gatter D8 (D 103) dient als Leitungstreiber gemäß der „K1520“-Vorschrift.

Bild 2 zeigt die fertige Schaltung. Bei den Autoren wurde diese gleich mit auf einer „K 1520„-kompatiblen Speicherkarte aufgebaut. Da das beschriebene RESET auf den Bus wirkt, muß nicht in den „Z 1013“ eingegriffen werden, wodurch das Systemkonzept gewahrt bleibt.

Literatur

[1] Kieser, Meder: Mikroprozessortechnik; Aufbau und Anwendung des Mikroprozessorsystems U880, 4.Auflage, Verlag Technik Berlin 1986, S.285