2025/11/04 12:30 1/8 Peters-Platine

# **Peters-Platine**

Autor: Jürgen Peters, IG Heimcomputer der TU Dresden

# **Anleitung / Handbuch**

Die im folgenden beschriebene Zusatzleiterplatte für den Mikrorechnerbausatz Z 1013 realisiert umschaltbar die Funktionen:

- Bildschirmformat 32\*32 oder 64\*16 (Zeichen\*Zeile)

- Taktfrequenz 2 oder 4 MHz

- Steuersignal für Umschaltung des Zeichengenerators

- Steuersignal für ROM-Abschaltung

- vollständige Dekodierung des I/O-Dekoders A 27

- Beschleunigung der Signale /CAS und /WR.

#### 1. Software-Schnittstellen

Für die softwaremäßige Umschaltung der einzelnen Zusatzfunktionen wurden D-FF (DL 074) eingesetzt, da es damit möglich ist, über die R/S-Eingänge das FF auch mit Tastern gegen Masse definiert zu setzen. Die D-Eingänge der vier FF liegen am Datenbus an D7, D6, D5 und D4. Diese Zuordnung wurde gewählt, weil durch A 47 (D 175) die anderen Datenleitungen bereits mit einer TTL-Last belegt sind. Für die Zuordnung der Datenbits wurden innerhalb der IG Heimcomputer Dresden folgende Festlegung, die als Normvorschlag gelten, getroffen:

- D7 Umschaltung des Bildformates 32\*32 oder 64\*16

- D6 Umschaltung der Taktfrequenz 2 MHz oder 4 MHz

- D5 Umschaltung des Zeichengenerators ( 2. Zeichensatz )

- D4 ROM-Abschaltung

Als I/O-Adresse wurde die 4 festgelegt. Weiterhin soll mit der Ausgabe des Datenbytes 00H auf die I/O-Adresse 4 der Grundzustand des Rechners (32\*32 Zeichen, 2 MHz, Originalzeichensatz und aktives Monitor-ROM) erreicht werden. Auf der gleichen I/O- Adresse ist das Rücklesen des aktuellen Zustandes (d. h. die Stellung der FF) möglich. Damit ist über AND- oder OR-Befehle ein definiertes Setzen oder mit XOR-Befehlen ein Umschalten der Funktionen einfach möglich. Für das Rücklesen wird ein DL 257 (VI 2) eingesetzt. Die Leitung /IOSEL 1 (Pin 2 von A 27) wird mit /RD oder /WR verknüpft und ergibt dann die Steuersignale zum Einspeichern des Datenwortes bzw. zur Durchschaltung der Q-Ausgänge der FF auf den Datenbus.

## 2. Funktion der Bildschirmumschaltung

Die Umschaltung des Bildschirmformates von 32 Zeilen mit 32 Zeichen in ein Format mit 64 Zeichen in 16 Zeilen ist vor allem für eine effektive Textverarbeitung erforderlich. Dabei sollte diese

Umschaltung software- und hardwaremäßig möglich sein. Das Prinzip beruht darauf, die Bildpunktfrequenz von 8 MHz auf 12 MHz zu erhöhen und einen Teiler für die Adressen des Bildwiederholspeichers von 1:2 in 1:3 umzuschalten. Damit werden in einer Fernsehzeile 64 Zeichen mit je 8 Punkten dargestellt. Die ausgenutzte Bildschirmbreite steigt damit auf 4:3 im Vergleich zum bisherigen guadratischen Bild und entspricht damit auch dem normalen Bildschirmformat. Mit dieser Schaltung wäre eigentlich eine Darstellung von 32 Zeilen mit jeweils 64 Zeichen einfach realisierbar. Es wurde aber darauf verzichtet, da dann ein doppelt so grosser Bildwiederholspeicher erforderlich wäre und die Lesbarkeit von Texten, für die diese Funktion ja in erster Linie gedacht ist, schlechter ist. Ausserdem wären wesentlich mehr Trennstellen auf der Leiterplatte erforderlich. Die graphischen Darstellungen erscheinen auch nicht sinnvoll, da die Zeichen verzerrt sind. Es werden hier die Zwischenzeilen dunkel getastet. Mit dieser Lösung sind auch kaum softwaremäßige Anpassungen erforderlich, da der Bildwiederholspeicher mit seiner Adressierung nicht verändert wird. Die Bildpunktfrequenz von 12 MHz wird mit einem LC-Oszillator erzeugt. Die Stabilität ist für diesen Anwendungsfall völlig ausreichend. Natürlich ist auch ein Quarz einsetzbar. Je nach Bildformat wird über die Gatterschaltung VI 10 entweder die 8 MHz- oder die 12 MHz-Bildpunktfrequenz gewählt. VI 3 bildet zusammen mit A 20 einen Teiler durch 3 (bei 64 Zeichen). VI 4 (DL 257) schaltet je nach gewähltem Format die entsprechenden Leitungen um. Der Ausgang 3 des freien Gatters von A 32 wird zum Ausgang 11 dieses Schaltkreises parallel geschaltet. An den Eingängen 1,2 wird das DunkelSteuersignal vom Multiplexer aus für die Zwischenzeilen gelegt. Durch die Negation des Bildsignals (einschließlich der Austastsignale) mit dem verbleibenden Gatter ist mit einem Umschalter auch schwarze Schrift auf weißem Grund möglich. Gegebenfalls ist für die negierte Darstellung R 26 zu vergrößern, um eine sichere Synchronisation des Fernsehgerätes zu erreichen, da durch die fehlenden Schwarzschultern das BAS-Signal nicht mehr normgerecht ist.

## 3. Taktumschaltung

Mit der wahlweisen Änderung der Bildpunktfrequenz muss die Rechnertaktfrequenz davon unabhängig erzeugt werden, da sonst die seriellen Schnittstellen (Tonband oder Drucker) nicht mehr funktionsfähig wären. Der 8 MHz-Quarztakt wird durch VI 9 durch 4 geteilt. über eine Torschaltung (VI 8) wird jeweils ein Aus- gang des FF auf die Taktleitung geschaltet. Mit dieser Konfigu- ration ist die softwaremäßige Umschaltung mit OUT-Befehlen sicher möglich. Eine manuelle Umschaltung der Taktfrequenz über die RS-Eingänge von VI 7 ist zwar möglich und im Muster auch vorgesehen, aber dabei tritt manchmal eine Verfälschung des RAM-Inhaltes ein.

## 4. Weitere Steuersignale

Für die Umschaltung des Zeichengenerators (z. B. mit negierter Darstellung bei gesetztem 7. Bit für die Kursordarstellung in Textsystemen) und des MEMDI-Signals für eine Abschaltung des ROM sind je ein FF der beiden Schaltkreise VI 3 und VI 1 vorgesehen. Durch Einbeziehung der Adressen A5, A6 und A7 sowie des negierten /M1-Signals für die Auswahl des I/O-Dekoders A 27 wird mit /IORQ eine vollständige Adressdekodierung mit VI 5 erreicht. Die letzte Funktion, die für den Betrieb des Rechners mit einer Taktfrequenz von 4 MHz erforderlich ist, geht auf eine Schaltung von Stölzer zurück. Auf der Leiterplatte ist dafür der VI 1 (1/2 DL 074) und die Verbindung mit /RD vorgesehen.

2025/11/04 12:30 3/8 Peters-Platine

#### 5. Hinweise zum Aufbau

Die Leiterplatte ist so konzipiert, dass sie über der Grund- leiterplatte mit 4 M2-Schrauben befestigt werden kann. Die Spule \*) des 12 MHz-Oszillators liegt dabei über dem Quarz. Für die erforderlichen Befestigungslöcher in der Grundplatte sind die Koordinaten (10;17,5) (10;52,5) (107,5;10) und (107,5;40) bezogen auf die Kontur der Leiterplatte mit dem (0;0)-Punkt an der Ecke mit dem Quarz vorgesehen. Es wurde versucht, mit einem Minimum an Leiterzugunterbrechungen auszukommen, obwohl die Zahl der erforderlichen Anschlüsse sehr hoch ist.

HINWEIS zur Spule: Minifilter 21 Wdg. Kern MF 330 orange

Neben der Entfernung der Brücke E2 für die Realisierung der vollständigen I/O- Dekodierung sind nur noch 4 Leiterzüge für die Umschaltung des Bildformates durchzutrennen. Der Einsatz eines 2732 für den Zeichengenerator erfordert weitere 2 Trennstellen, da die /CS-Leitung doppelt an 5V geführt ist. Die Beschleunigung der Signale /CAS und /WR nach Stölzer erfordert eine weitere Trennstelle. Für den Aufbau ist es zweckmäßig, zunächst die Leiterplatte vollständig zu bestücken und mit einer separaten Stromversorgung den Oszillator auf 12 MHz voreinzustellen. Die typische Stromaufnahme der Schaltung liegt bei 50 mA. Danach ist ein stufenweiser Einbau günstig. Zuerst werden die vier Trennstellen für die Bildformatumschaltung angebracht. Die Brücke E1 für den Takt wird auch entfernt. Nach den Anschlüssen für die Umschaltung des Bildformates und des Taktes wird diese Funktion geprüft, indem das zugehörige FF (VI 7) manuell umgeschaltet wird. Wenn die Änderungen an A 32 noch nicht erfolgt sind, werden die Zeilen bei 64 Zeichen doppelt geschrieben. Wenn dieser Teil richtig funktioniert, werden die Datenleitungen D4 ... D7 sowie /RD , /WR und /IOSEL 1 angeschlossen. Nach einer Funktionsüberprüfung dieses Arbeitsstandes wird die Beschleunigung der Signale /CAS und /WR realisiert. Mit den einfachen Testprogrammen

```

INIT:

LD A,00H

; 3E 00

0UT 4

: D3 04

RST 38

; FF

LD A.OFFH

3E FF

NEGAT:

0UT 4

; D3 04

RST 38H

; FF

UMSCH:

IN 4

; DB 04

CPL

: 2F

; D3 04

0UT 4

RST 38H

; FF

```

kann die Funktion der softwaremäßigen Umschaltung überprüft werden. Als letztes wird die vollständige I/O-Dekodierung realisiert.

Der Aufbau dieser Schaltung und die Belebung erfordern eine ausreichende Schaltungskenntnis des Mikrorechnerbausatzes und der Funktion der Bilderzeugung, so dass der Nachbau nur dem versierten Amateur empfohlen wird. Die relativ geringe Zahl von auf der Leiterplatte zu trennenden Leiterzüge ermöglicht die industrielle Reparatur, indem die Trennstellen überbrückt werden und alle zusätzlichen Anschlüsse wieder entfernt werden. Bauelemente bzw. Gatter, die auf der Grundleiterplatte bereits vorhanden sind, sind im Schaltbild gestrichelt dargestellt und entsprechend der Stromlaufpläne gekennzeichnet. Beim Entwurf des Layoutes wurden die nicht benötigten Eingänge (A0 ... A3) des Multiplexers DL 257 (A2) mit für Verbindungen genutzt, um eine einfachere Leiterzugführung zu erreichen. Der Ersatz von L1 und C1 durch einen Quarz ist im Leiterzugbild berücksichtigt.

#### Aufbauhinweise Stand: 16. 4. 1989

Zur Erleichterung des Nachbaues folgen noch einige Hinweise:

- Für die Betriebsspannung und Masse sind keine extra Anschlüsse auf der Platte gekennzeichnet (die Leiterzugführungen auf der Bestückungsseite eignen sich dafür).

- Die Spule L1 hat 21 Wdg. (Minifilter Mf 330). Zum leichteren Abgleich der 12 MHz bei anderen Spulendaten ist für C1 die Parallelschaltung eines zweiten Kondensators auf der Leiterplatte vorgesehen.

- C5 und C6 unterdrücken Spikes, die durch Gatterlaufzeiten entstehen und sichern so das exakte Teilerverhältnis.

- Die Anschlüsse x40 und x41 stellen die Signale /RD und /WR noch einmal getrieben für weitere Erweiterungen bereit. Sie sind im Muster nicht angeschlossen.

- Die FF für die Zeichengeneratorumschaltung bzw. für die ROM-Abschaltung speichern nur die Ansteuersignale für diese Erweiterungen. Die entsprechende Schaltungsauslegung ist individuell zu lösen.

- x11 (/RESET) wird parallel zum /RESET der CPU angeschlossen.

- Die Anschlüsse x12 bis x23 der Speicher-FF brauchen nur bei Bedarf angeschlossen werden. (Die Eingänge, wenn manuell über Schalter umgeschaltet werden soll und die Ausgänge, wenn die entsprechenden Erweiterungen angesteuert werden.)

- Die etwas dunkleren Streifen der dunkelgestasteten Zeilen sind auf die niedrigere Impedanz der parallel geschalteten Ausgänge von A 32 zurückzuführen. Wenn es stört, muß das Signal noch einmal durch ein Gatter getrieben werden. Bei der negierten Darstellung tritt der Effekt schon nicht mehr auf.

- Werden einzelne Funktionen nicht genutzt (z. B. Taktfrequenzumschaltung), so sollten die entsprechenden Eingänge des Muxers für das Rücklesen auf L-Potential gelegt werden. Sonst kann beim Rücklesen eine falsche Konfiguration erkannt werden, die bei der seriellen Schnittstelle zur falschen Zeitkonstanten oder beim Bildschirmdruck zum falschen Druckformat führen kann.

- Die Schaltung wurde bereits mehrfach erfolgreich aufgebaut. Dabei wurden Schaltkreise verschiedener Hersteller (DDR, SU) verwendet. Zu beachten ist, daß in der Nähe der Oszillatorspule keine Leitungen mit größeren Wechselströmen (Betriebsspannungszuführungen vom und zum Netztrafo) verlaufen, da es durch das Wechselfeld zu Frequenzmodulationen mit der Netzfrequenz führt. Dadurch können Bildstörungen (Verzerrungen) auftreten. Die Bauelementewerte sind ziemlich unkritisch. Lediglich die Oszillatorfrequenz muß sich auf 12 MHz einstellen lassen und die Amplitude muß so groß sein, daß am Gatterausgang (Pin 8) von VI 10 eine möglichst symmetrische Spannung entsteht.

- Der Masseanschluß für die Zusatzbaugruppe ist mit großem Querschnitt auszuführen, andernfalls kann es im 64-Zeichenmodus zu einem unstabilen Bild kommen.

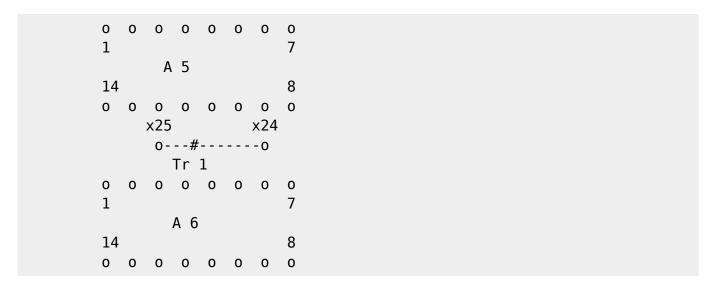

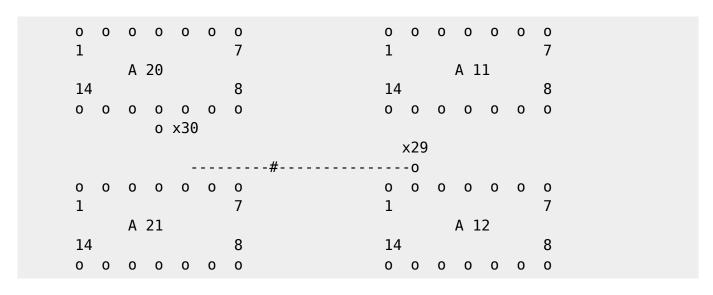

• Die Trennstelle für die Beschleunigung von /CAS und /WR wurde schon oben beschrieben. Für die einzelnen Trennstellen Tr 1 bis Tr 4 wird versucht, die durchzutrennenden Leiterzüge auf der Leiterplatte zu beschreiben. Dazu werden gegebenfalls die wesentlichen Lötaugen symbolisch dargestellt. Das Doppelkreuz ( # ) symbolisiert die Trennstelle.

**Tr 1**: Trennen des Leiterzuges auf der Leiterseite zwischen den Schaltkreisen A 5 und A 6. Die beiden anliegenden Durchkontaktierungen ergeben die Anschlüsse x24 und x25:

**Tr 2**: Trennen auf der Leiterseite bei A 20 zwischen Pin 10 und Pin 13. Der Anschluß von x27 erfolgt entweder auf der Leiterseite oder auf der B-Seite direkt am Pin 10.

**Tr 3**: Trennen auf der Leiterseite: Der schräge Teil des zu unterbrechenden Leiterzuges zu dem Lötauge, das für den Anschluß x30 genutzt werden, kann aus drucktechnischen Gründen nicht dargestellt werden.

**Tr 4**: Der Leiterzug muß auf der B-Seite durchtrennt werden. Für x32 kann das Lötauge zwischen Masseleitung und Pin 7 von A 42 genutzt werden. Die Trennstelle liegt zweckmäßig zwischen A 43 und A 44, wo der Leiterzug mit größerem Abstand parallel zur Masseleitung verläuft. Der Anschluß x31 kann entweder auf diesem Leiterzug oder direkt am Pin 11 von A 5 erfolgen.

Der Aufbau dieser Schaltung und die Belebung erfordern eine ausreichende Schaltungskenntnis des Mikrorechnerbausatzes und der Funktion der Bilderzeugung, so daß der Nachbau nur dem versierten Amateur empfohlen wird. Die relativ geringe Zahl von auf der Leiterplatte zu trennenden Leiterzüge 11:44

ermöglicht die industrielle Reparatur, indem die Trennstellen überbrückt werden und alle zusätzlichen Anschlüsse wieder entfernt werden.

ACHTUNG: Im Layout der Leiterplatte ist erst jetzt (April 89) ein Fehler festgestellt worden. Der nichtnegierte Ausgang von VI 1 des Flip-Flop für die ROM-Abschaltung (Pin 9) muß mit Pin 13 von VI 2 verbunden werden. Auf der Leiterplatte ist irrtümlich Pin 8 anstelle von Pin 9 von VI 1 angeschlossen. Das geänderte Layout ist mit " 1.1" gekennzeichnet. Dieser Fehler führt beim Rücklesen des Zustandes zu einer falschen Aussage und bei der Ausgabe dieses Wertes wird dann das Flip-Flop falsch gesetzt. Dieser Layoutfehler ist auch noch in den Lichtpausen des Tagungsmaterials enthalten.

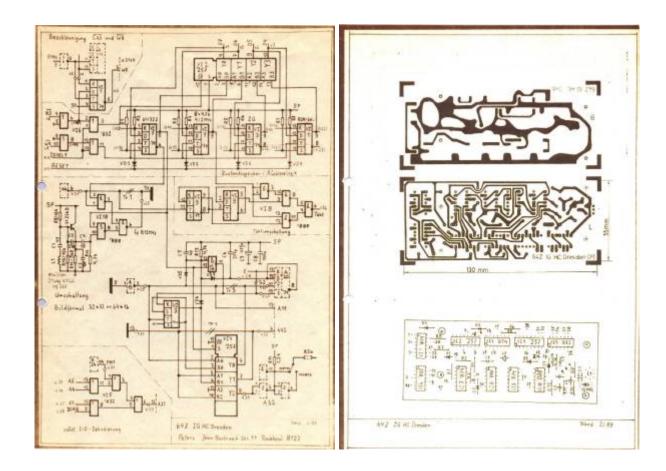

# Schaltungsunterlagen

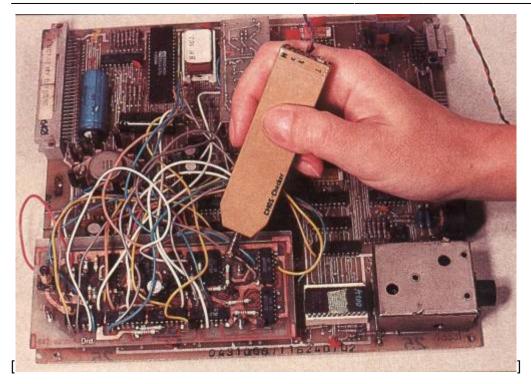

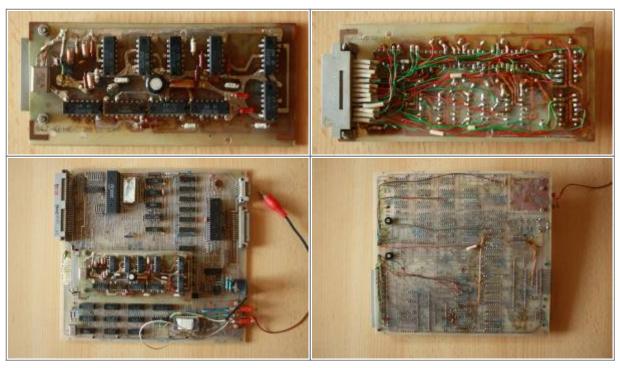

## **Aufbau**

2025/11/04 12:30 7/8 Peters-Platine

sauberer, wenn auch ungewöhnlicher Aufbau

# **Hinweise**

Auf der Leipziger Nachtagung gab es folgende Hinweise zum Aufbau:

- Fehler: VI 1 Pin 8 → Pin 9 Anschluss auf LP ändern. In Schaltung richtig.

- am Bustreiber an A 41 Adr. 2 abklemmen, sonst Fehler beim Rücklesen IN 4

- große Masseleitung zu Grundplatine (1mm²)

• CAS-Beschleunigung über 4 MHz, nicht 8 MHz.

From:

https://hc-ddr.hucki.net/wiki/ - Homecomputer DDR

Permanent link:

https://hc-ddr.hucki.net/wiki/doku.php/z1013/erweiterungen/petersplatine?rev=1317642284

Last update: 2011/10/03 11:44